# Accelerating Time-to-Money for a Semiconductor Wafer Fab Capacity Ramp

# by Christopher K. Keith

S.B. Materials Science and Engineering, M.I.T., Cambridge, MA, 1991

Submitted to the Sloan School of Management and the Department of Materials Science and Engineering in partial fulfillment of the requirements for the degrees of

## Master of Science in Management and Master of Science in Materials Science and Engineering

## at the Massachusetts Institute of Technology June 1996

(c) Massachusetts Institute of Technology, All rights reserved

| Signature of Author |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | Sloan School of Managemen<br>May 10, 1990                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Certified by        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ,                   | Professor Rebecca Henderson, Thesis Adviso Sloan School of Managemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Certified by        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                     | Stanley Gershwin, Senior Research Scientist, Thesis Adviso<br>Department of Mechanical Engineering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Certified by        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| •                   | Professor Lionel Kinnerling, Department Reade<br>Department of Materials Science and Engineering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Accepted by         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                     | Jeffrey A. Barks, Associate Dear School Scho |

| Accepted by         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| . ,                 | Professor Michael Rubner, Chairman Department Committee on Graduate Student                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                     | MASSACHUSETTS INSTITUTE  OF TECHNOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

JUN 1 4 1996

ARCHIVES

## Accelerating Time-to-Money for a Semiconductor Wafer Fab Capacity Ramp

by

## Christopher K. Keith

Submitted to

the MIT Sloan School of Management and

the Department of Materials Science and Engineering

in Partial Fulfillment of the Requirements for the Degrees of

Master of Science in Management and Master of Science in Materials Science and Engineering

#### **ABSTRACT**

Companies in the semiconductor industry plan to build over one hundred semiconductor fabs during the next four to five years. Each of these fabs requires approximately one to two billion dollars of investment. The pressure to quickly get the fab up and running and recover the initial investment is enormous. The pressure is most intense during the factory start-up, also referred to as the capacity ramp.

This thesis focuses on identifying factors that influence the success of a semiconductor fab start-up. Data on semiconductor fab start-ups was gathered from several sources within Intel Corporation for the purpose of better understanding these factors. The data includes both quantitative data, such as wafer starts, yield, and headcounts, and qualitative data that was gathered during interviews with fab personnel who had been involved with previous fab start-ups. In addition, more detailed analysis was undertaken concerning equipment installation schedules for a fab start-up. Four different equipment installation schedules, each based on a different strategy, were compared using a discrete-event simulator. The results of the simulation are also presented and discussed.

The analysis suggests that there are many important factors that determine the success of a semiconductor fab start-up. Examples of important factors include staffing and training, equipment installation, and process capability. The relevance of the results to start-ups at semiconductor fabs in other companies and to factory start-ups in other industries is discussed.

#### Thesis Advisors

Dr. Rebecca Henderson, Professor, MIT Sloan School of Management

Dr. Stanley Gershwin, Senior Research Scientist, Mechanical Engineering Department

Dr. Lionel C. Kimerling, Professor, Materials Science and Engineering

The author gratefully acknowledges the support and resources made available to him through the MIT Leaders for Manufacturing Program, a partnership between MIT and major U.S. manufacturing companies.

3

,

#### **Acknowledgments**

This thesis was far from an individual effort. Many people played significant roles in all phases of the thesis. Without the assistance of numerous people at Intel, MIT professors, students, and others, the data analysis would have suffered. It would be impossible to list everyone who influenced my thinking, both before and during the thesis, but I would like to thank the most significant contributors.

Special thanks go to Don Myers for initiating and supporting this internship at Intel. His willingness to try new things provided me with the opportunity to explore many different areas that were not strictly related to the Operations Group.

I am thankful to Rich Watkins and the entire Manufacturing Engineering Group at D2, including Paul Sura, Rick Schmidley, and Ralph Kiuttu. Rich and the rest of his staff provided valuable guidance, support, and data for focusing my research efforts. Many thanks go to Jacques Vuye for his help and support throughout the internship.

I would also like to thank my thesis advisors, Professor Rebecca Henderson and Professor Stanley Gershwin, for providing me with very valuable support and guidance and for keeping me focused on the bigger picture. Their critical analysis and pertinent comments greatly aided my thinking. In addition, I am very grateful to Professor Lionel Kimerling for his time and effort in reviewing the draft and providing helpful comments.

Lastly, I thank my parents for their support and encouragement throughout my life. They encouraged me to keep learning and get an education.

## **Bibliographical Note on Author**

Christopher K. Keith was graduated from the Massachusetts Institute of Technology, Cambridge, MA in June 1991 with a Master of Science degree in Materials Science and Engineering. Chris joined Intel Corporation in July 1991 and worked in various process engineering roles at Intel Mask Operations (IMO) in Santa Clara, California. Upon his acceptance to MIT's Leaders for Manufacturing program, Intel Corporation decided to sponsor him, and he will be joining Intel's Technology and Manufacturing Group in July 1996. He is currently working towards masters degrees in management and materials science and engineering and expects to graduate in June 1996.

## **Table of Contents**

| 1.0  | Introduction                                                                   | 11 |

|------|--------------------------------------------------------------------------------|----|

| 2.0  | Problem Statement and Research Methodology                                     | 13 |

|      | 2.1 Problem Statement and Project Motivation                                   | 13 |

|      | 2.2 Research Methodology                                                       | 14 |

| 3.0  | Literature and Theory Review                                                   | 15 |

|      | 3.1 Review of Literature on Semiconductor Fab Start-ups                        | 15 |

|      | 3.2 Review of Production Theory                                                | 17 |

|      | 3.3 Literature Review of Capacity Expansion                                    | 18 |

|      | 3.4 Overview of Semiconductor Device Fabrication                               | 22 |

|      | 3.5 Characteristics of Semiconductor Manufacturing Systems                     | 25 |

| 4.0  | Factors Affecting the Semiconductor Fab Start-up                               | 27 |

| 5.0  | Data and Methods                                                               |    |

|      | 5.1 Historical Data                                                            | 31 |

|      | 5.2 Data for the Discrete-Event Simulator                                      |    |

| 6.0  | Intel History and Characteristics of Intel Fabs                                | 36 |

|      | 6.1 Intel's Strategy and Position in the Semiconductor Industry                | 36 |

|      | 6.2 Understanding Intel's Capacity Planning and WIP Management Strategies      | 39 |

|      | 6.3 Background and Introduction to Intel's Fab A                               | 41 |

| 7.0  | Analysis of Data                                                               | 43 |

|      | 7.1 Analysis of Data from Fab A                                                | 43 |

|      | 7.2 Analysis of Comparison Data from the Ramps at Fab A and Fab C              | 52 |

|      | 7.3 Analysis of External Benchmarking Data                                     | 53 |

|      | 7.4 Limiters to the Start-up at Fab A                                          | 54 |

| 8.0  | Analysis of a Capacity Addition Policy that Includes the Effect of Disruptions | 56 |

| 9.0  | Factory Simulation Model for the 0.25 Micron Technology Ramp at Fab A          | 62 |

| 10.0 | Trade-off Between Availability and Die Yield at the Capacity Constraint        | 68 |

| 11.0 | Results of Data Analysis                                                       | 71 |

| 12.0 | ecommendations for Improving the Upcoming Ramp at Fab A                        |    |

| 13.0 | Extension of Results to Start-ups in Other Industries                          | 75 |

| 14.0 | Reflection on Process and Future Direction                                     | 77 |

|      | Appendices                                                                     | 79 |

|      | Bibliography                                                                   | 83 |

# **List of Figures**

| Figure 3.1  | Capacity Expansion Strategy Where Capacity Leads Demand                                                  | 19   |

|-------------|----------------------------------------------------------------------------------------------------------|------|

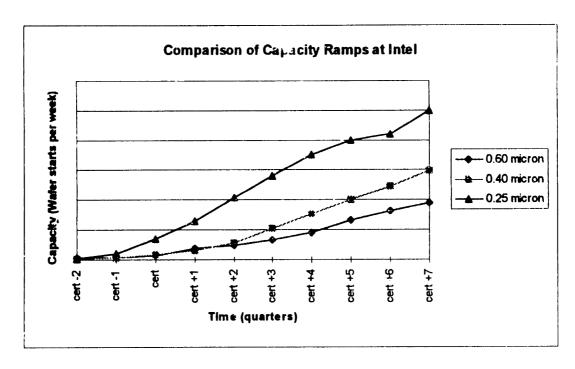

| Figure 6.1  | Comparison of Capacity Ramps at Intel                                                                    | 38   |

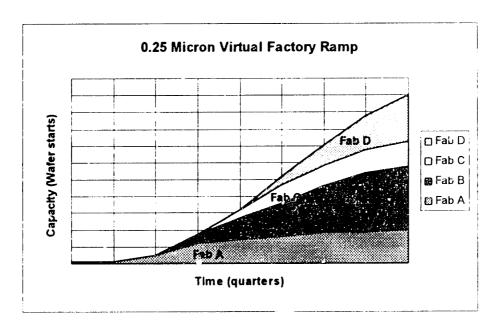

| Figure 6.2  | 0.25 micron technology generation Virtual Factory Capacity Ramp at Intel                                 | 42   |

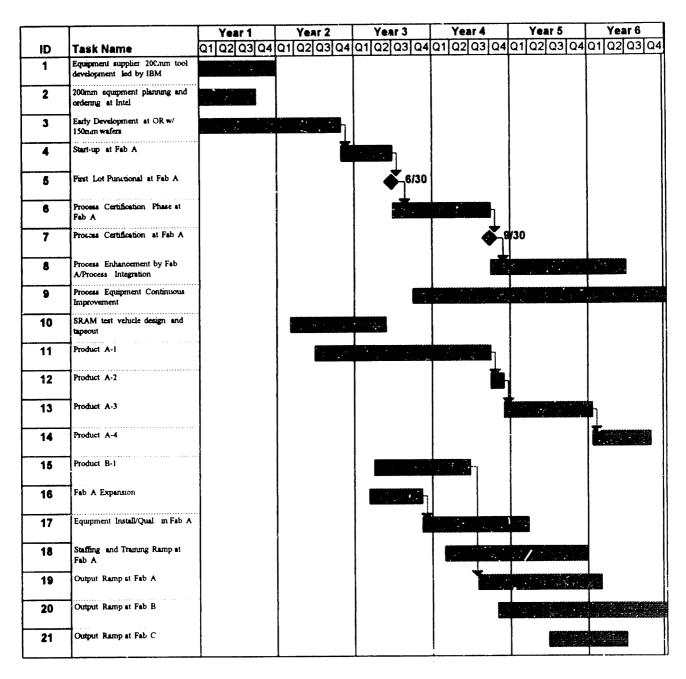

| Figure 7.1  | 0.6 Micron Process Technology Generation Gantt Chart                                                     | 45   |

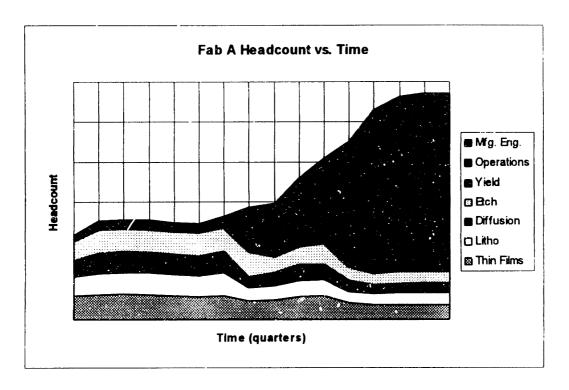

| Figure 7.2  | Headcount ramp at Intel's Fab A                                                                          | 46   |

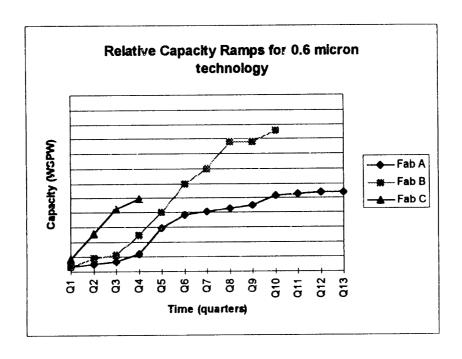

| Figure 7.3  | Capacity Ramps for Intel Fabs for the 0.6 micron process technology  Generation                          | 47   |

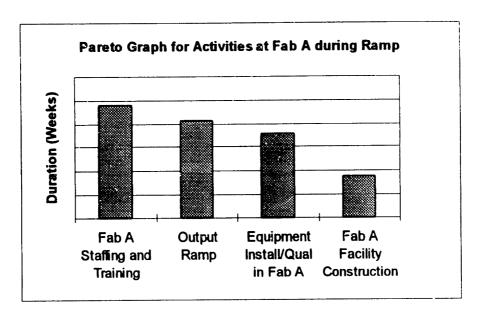

| Figure 7.4  | Pareto of activities during ramp at Intel's Fab A                                                        | 48   |

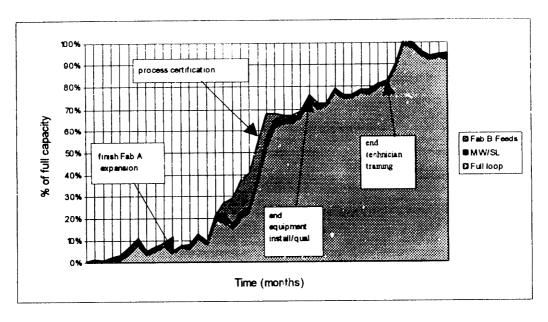

| Figure 7.5  | Activity Milestones vs. Wafer Starts per Week (WSPW) Ramp at Fab A                                       | 49   |

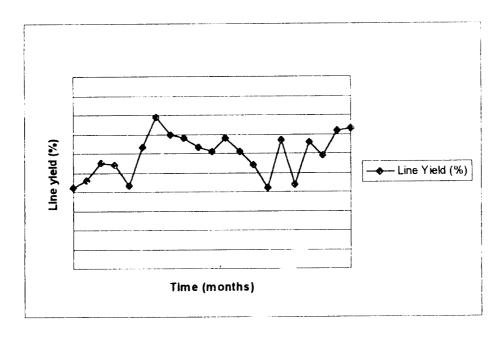

| Figure 7.6  | Line Yield during Start-up at Fab A                                                                      | . 49 |

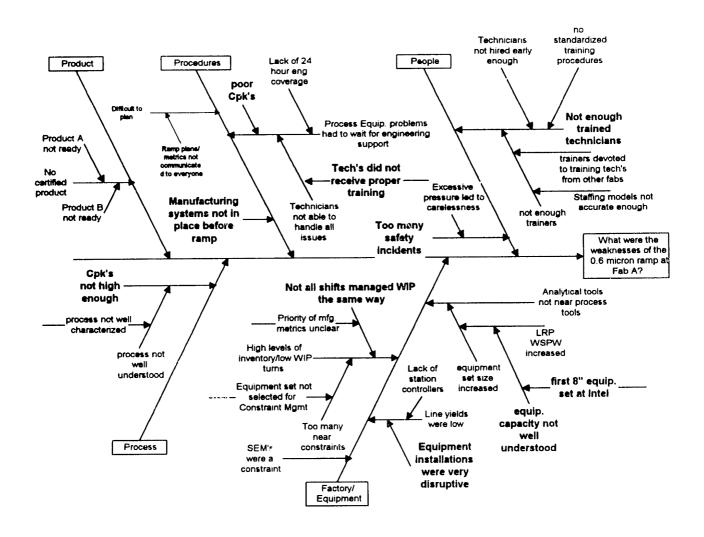

| Figure 7.7  | Cause-and-Effect Diagram for 0.6 Micron Technology Generation Ramp at Intel's Fab A                      | . 51 |

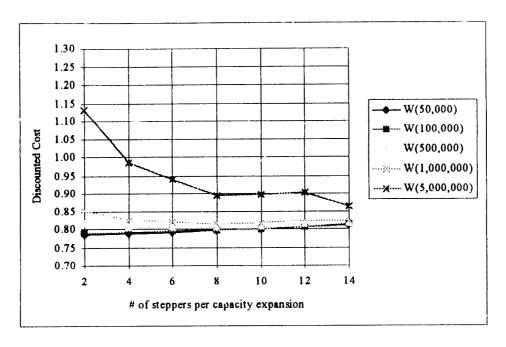

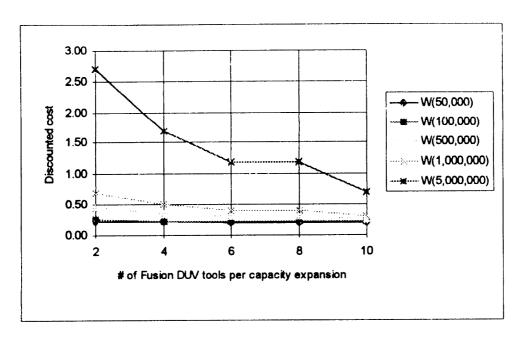

| Figure 8.1  | Sensitivity Analysis and Cost Comparison of Stepper Expansion Scenarios for Medium-Sized Fab.            | . 59 |

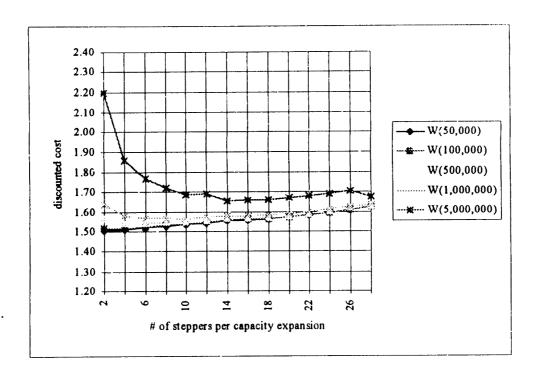

| Figure 8.2  | Sensitivity Analysis and Cost Comparison of Stepper Expansion Scenarios for a Large Fab.                 | 60   |

| Figure 8.3  | Sensitivity Analysis and Cost Comparison for an inexpensive process equipment tool at a Medium-Sized Fab | . 61 |

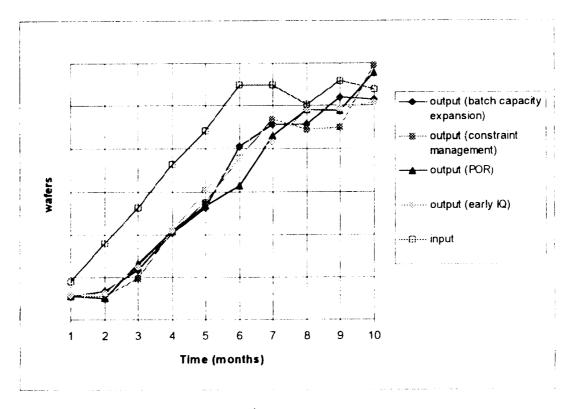

| Figure 9.1  | Factory Output Comparison of Equipment IQ Strategies                                                     | . 64 |

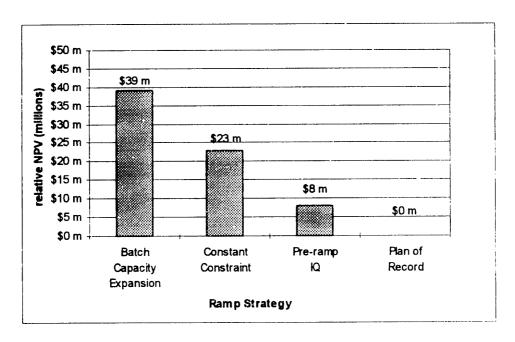

| Figure 9.2  | NPV Comparison of Equipment IQ Strategies                                                                |      |

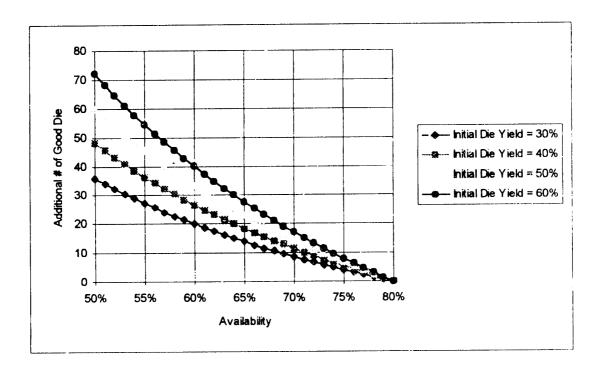

| Figure 10.1 | Trade-off Curve for Availability and Die Yield Improvements                                              |      |

#### Chapter 1. Introduction

Continued growth in the semiconductor industry, which has been driven by 30% annual growth rates in the personal computer industry during recent years, has led to an ambitious capital spending program by semiconductor manufacturers all over the world. The high growth rate in the semiconductor industry and the need to advance chip performance through the introduction of ever smaller geometries and more complex processes means that semiconductor companies must invest huge sums of money just to maintain their competitive position relative to their competitors. In order to keep pace with projected demand, over 100 new semiconductor fabrication plants, also known as fabs, are planned through the end of the decade. With each of these fabs costing over \$1 billion to build and equip, the construction of all of these new factories represents an enormous commitment of capital and resources on the part of the semiconductor industry.

Typically, a new factory is expected to be up and running quickly, so that it can meet the firm's immediate eeds and provide a solid base on which to expand and become increasingly profitable. The wility of a new factory to get up and running quickly in the semiconductor industry is especially critical since the typical productive life cycle of a semiconductor fab is on the order of 4 - 6 years. Contrast that with an automotive engine plant, which is expected to last for 20 years or more. Or chemical plants, whose life cycle is also on the order of 20 or more years. Given a life cycle of about five years, the percentage of time that a semiconductor fab spends in the start-up phase is clearly a larger percentage of its life cycle than a new plant in any other industry. In fact, it is not unusual for a semiconductor fab to spend 10% to 20% of its life cycle in the start-up phase.

Given the huge initial fixed costs, between \$1 billion and \$2 billion, required to build and equip a state-of-the-art semiconductor fab, and the relatively short life cycle of the fab, it is very important for the fab to begin generating revenue as quickly as possible. As a result, one of the most critical periods of time during a fab's life cycle is the start-up, or ramp phase. The ramp phase is a period of time that can last from six to twenty four months during which all the process equipment is being installed and qualified for production and the number of wafers being released into the factory is increasing rapidly. It is during the ramp that the fab begins to generate revenue through the production of functional semiconductor devices.

My thesis focuses on the fab start-up and how to improve it. My goal is develop a framework based on the literature and theory for understanding some of the factors that affect the success of a semiconductor fab ramp and then compare that framework with historical data gathered from actual semiconductor fab start-ups. Most of my data on actual start-ups is gathered from fabs at Intel Corporation. My research is focused on understanding the factors that affect the start-up of a new semiconductor fab and using that information to make recommendations for improving an upcoming ramp at an Intel fab. The primary customers for my thesis are plant managers and operations managers at semiconductor fabs.

The remainder of the thesis is divided into thirteen chapters. Chapter Two presents the problem statement and research methodology. Chapter Three reviews the theory and literature

relevant to the problem statement. Chapter Four summarizes the factors that might affect the performance of a semiconductor fab start-up. Chapter Five discusses the data sources and data collection process. Chapter Six presents a brief summary of Intel's current strategy and discusses some of the characteristics that may be unique to Intel fabs. The data on start-ups collected from Intel fabs is analyzed in Chapter Seven. Chapter Eight goes into more detail concerning the results generated in Chapter Seven that relate to equipment installation. Several capacity expansion strategies for an upcoming fab ramp at Intel are analyzed and compared in Chapter Nine. Chapter Ten presents an analysis of the trade-off between capacity and die yield at the constraint. The results of the analysis are summarized in Chapter Eleven. Specific recommendations for an upcoming start-up at an Intel fab are presented and discussed in Chapter Twelve. Chapter Thirteen discusses the extension of the results to factory start-ups in other industries. Chapter Fourteen considers how the problem-solving process could have been better executed and provides direction for future work and projects. The Appendices and Endnotes can be found after the last chapter.

## Chapter 2. Problem Statement and Research Methodology

This chapter presents the problem statement of my thesis and discusses the methodology that was used to research the problem.

## 2.1 Problem Statement and Project Motivation

My research is concerned with the problem of managing a start-up at an individual semiconductor fab, as opposed to managing capacity expansion at the firm level. This thesis focuses on factors affecting the success of the semiconductor fab start-up. The goal is to identify and understand some of the levers that influence the performance of a semiconductor fab start-up.

As described in the previous chapter, the semiconductor industry has experienced double-digit growth during the last several years. Most semiconductor manufacturers are finding that their current capacity does not meet the increasing demand. The forecast for continued growth, combined with the need for more advanced process technologies, has resulted in an extensive industry-wide capacity expansion. The planned investment in new semiconductor fabs during the next four to five years is expected to be over \$100 billion.

Each of these new fabs must go through a sometimes tortuous process call the ramp. The ramp is the period of time after which the fab is completed and during which equipment is being installed, processes are being developed and tested, and the first product is being manufactured. It is during the ramp that the fab begins to generate revenue. The ramp is critical because up until the ramp phase, the fab is a huge money sink. By the time that the first product wafers are processed, from \$1 billion to \$2 billion has been spent to build, equip, and staff the fab. As the ramp proceeds, the initial investment can be recovered, assuming that the ramp proceeds smoothly and as planned. If the ramp does not proceed smoothly, the return on the rather large initial investment can be significantly reduced.

Time and money, as measured by the speed with which the fab ramps output and hence revenue, are extremely important metrics for a semiconductor fab start-up. Over time, the initial investment can be recouped and the fab can become profitable when cumulative discounted revenue exceeds cumulative discounted cost. The faster the fab can ramp without problems, the faster the initial investment can be recovered, assuming that demand for the product is relatively elastic. If demand is not price-elastic, then it may be difficult to sell additional product from the faster ramp.

What is required for a fab start-up to be successful? How should the fab allocate its limited resources to maximize performance during the ramp? What can be done before and during the start-up to ensure continued success after the start-up phase? These are questions that face the management team of a new semiconductor fab. The purpose of this thesis is to help answer some of these questions by understanding some of the levers or activities that are most important to the success of a fab start-up.

#### 2.2. Research Methodology

This section describes the methodology that was used to investigate and research the problem statement. The research on semiconductor fab start-ups was divided into several steps. The steps were:

- 1. Review the literature

- 2. Identify levers that might affect the performance of a semiconductor fab start-up

- 3. Perform in-depth analysis on a recent semiconductor fab start-up

- 4. Analyze ramps at other semiconductor fabs

- 5. Compare equipment installation strategies for the start-up phase

- 6. Model the trade-off between capacity and yield at the factory constraint

The first step was to review the current literature and theory to develop a framework for understanding semiconductor fab start-ups. The framework was used to identify a list of factors that might affect the performance of a semiconductor fab ramp. Once the factors were identified, historical data from a start-up at an Intel fab - hereafter referred to as Fab A - was analyzed. Additional data was gathered from a more recent ramp at another Intel fab - hereafter referred to as Fab C. Benchmark data from a fab start-up at another semiconductor manufacturer was also analyzed. The factors that were identified in step two were compared and contrasted to the data that was gathered from several actual semiconductor fab start-ups.

The last two steps were attempts to take what had been learned about semiconductor fab startups and apply that learning to an upcoming ramp at Fab A. First, several different equipment installation strategies were compared using data from an upcoming ramp at Intel's Fab A. An equipment installation schedule was generated for each of the strategies and then compared using a simple discrete-event simulation model. Last, a simple model was built to investigate the tradeoff between wafer capacity and die yield at the fab's constraint.

# Chapter 3. Literature and Theory Review

This chapter reviews literature on semiconductor fab start-ups. The purpose of the literature and theory review is to help develop a framework for understanding and analyzing semiconductor fab start-ups. The relevant literature and theory included information on:

- 1. semiconductor fab start-ups

- 2. the production function

- 3. capacity expansion

- 4. semiconductor manufacturing systems

### 3.1 Review of Literature on Semiconductor Fab Start-ups

Literature and database searches revealed a limited amount of information and theory concerning semiconductor factory ramps. There were no literature that presented a complete overview of ramping a semiconductor factory; however, there were several sources of information that discussed certain aspects of the start-up. Benfer [1] provided an excellent source of information for some of the critical issues affecting semiconductor factory ramps. The thesis discussed the importance of die yield and yield learning as levers in improving output during a semiconductor fab ramp. The thesis investigated how characteristics of a semiconductor fab start-up, such as noise and variability, affected the ability of the fab to make improvements in die yield. One recommendation that was made was to install capacity in larger chunks during the ramp to minimize the disruptions due to equipment installation and qualification. My thesis builds on this work by applying some level of analytical rigor to the decision regarding the size and timing of capacity installations. Many of the themes discussed by Benfer were used to aid the analysis of capacity expansion strategies in Chapter Seven of this thesis.

Bohn [2] briefly discussed the importance of understanding and managing technological knowledge during ramp-up of new production in high-tech industries. In the paper, Bohn provided a framework to measure how much the firm knows and does not know about its production processes. The framework was a scale of eight stages of knowledge that is useful for measuring knowledge about a process. Stage One represented complete ignorance; while, Stage Eight was complete knowledge. Bohn applied the scale to high-tech manufacturing, such as VLSI semiconductor design and fabrication processes, which requires rapid learning about multiple variables in new products and processes. Since VLSI semiconductor fabrication is very complex and the process is difficult to control, a lot of effort and resources go into raising the knowledge level as quickly as possible. Bohn concluded that "managing in high-tech industries requires both rapid learning and the ability to manufacture with "immature" (low state of knowledge) technologies." [3]

Because of the limited amount of literature on semiconductor factory ramps, the scope of the literature search was widened to include start-ups in any industry. This literature search led to little additional information. While there was quite a bit of literature that discussed capacity expansion and factory planning and start-ups from a corporate-wide, strategic perspective, there

was a relatively small amount of information and literature that dealt with the issues faced by plant management during factory start-ups in any industry.

Most of the relevant literature on factory start-ups referenced or built on an article by Schmenner[4]. Schmenner discussed the three phases of the a plant's life cycle - the start-up and early years, the mature years, and the failing years. In addition to discussing plant responsibilities during the start-up and early years, the article described some of the issues that affected the success of the plant's start-up phase. The issues identified included:

- 1. Plant engineering

- 2. Work force

- 3. Overhead functions

- 4. Control systems

Plant engineering includes decisions on factory area, configuration, equipment choice, flow patterns of the products within the plant, materials handling, utilities, environmental regulation compliance, and similar tasks. Schmenner believes that the engineering of a new facility is critical and that it is probably the start-up aspect that manufacturing companies handle most expertly.

Work force issues include the size of the work force, the mix of skill levels, and recruiting and training plans. The article states that in order to smooth the transition to the new plant and speed the start-up, companies may want to begin labor training before the plant opens. Other issues that involve the work force are wage schemes and decisions that affect the hierarchy of the work force, such as the use of self-directed work teams.

Since most new plants do not have in place a full complement of overhead functions in their first years, plant management must decide which overhead functions it will undertake itself and which will be left to headquarters or another plant's staff. Overhead functions include new product engineering, raw materials purchasing, industrial engineering, and production planning.

Control systems are also critical to start-up success. Too often during start-ups, companies neglect the production and inventory control, accounting, and quality control systems. These systems are important because they yield good information about how well the facility is performing. This information can be used to direct continuous improvement activities during all stages of the factory's life cycle.

Other than the three articles discussed in this section, there was very little literature about factory start-ups. The exact reasons for the lack of literature are not known; however, the lack of literature could lead one to conclude that the area of factory start-ups is a fertile area for future research.

#### 3.2 Review of Production Theory

The absence of literature on semiconductor factory ramps, or factory start-ups in general, meant that other areas of theory had to be relied upon to establish a framework for trying to understand the problem statement. In order to understand some of the factors that might affect a semiconductor fab start-up, the literature on production theory was reviewed. The remainder of this section draws from Chapter Six of Pindyck [5].

Production theory attempts to model the relationship that describes how firms transform inputs (such as labor and capital) into outputs (such as cars and integrated circuits). This relationship is typically represented in the form of a production function. The production function is used to show how the firm's output changes when first one and then all the inputs are varied. A production function indicates the output Q that a firm produces for every specified combination of inputs. A simple model might include only two inputs, labor L and capital K. If these are the only two inputs, the production function can be written as

$$Q=F(K,L)$$

This equation relates the quantity of output to the quantities of the two inputs, capital and labor. Each of these broad categories (capital and labor) might include more narrow subdivisions. Labor inputs include skilled workers and unskilled workers. Capital includes buildings, equipment, and inventories. In addition, we could add other broad categories such as materials to the production function to improve its accuracy.

Production functions can take many forms. One of the most common is the Cobb-Douglas production function. The Cobb-Douglas production function is

$$F(K,L) = AK^{\alpha}L^{\beta}$$

Another example of a production function is

$$F(K,L) = AK + BL$$

These production functions were generated by fitting equations to historical data.

The production function of a semiconductor factory process technology is very complex. The output of a semiconductor fab is good die. A die is an individual integrated circuit chip. Inputs include silicon wafers, which are the raw material for the dies, the number of factory operators and engineers, the amount of installed equipment, and the square footage of the semiconductor fab.

The purpose of this thesis is not to develop explicit models for production functions in semiconductor fabs; however, the analysis does draw upon some of the basic concepts of the production function. The most important concept is that inputs and outputs are related by some physical relationship which can be described with a mathematical model. In the case of a

semiconductor fab, the most important physical inputs include silicon wafers, work force size, and capital equipment. One complicating factor is that silicon wafers can be treated as either an input or an output. Silicon wafers go into the process at one end of the factory and silicon wafers come out at the other end of the factory. One silicon wafer can hold anywhere from fifty to several hundred die.

The main weakness of the production function is that it is a static model. The production function captures the state of the process technology at a given point of time. However, semiconductor fab ramps are inherently dynamic and much more complex than the production function model allows. As a result, there are some important factors that affect the factory ramp that the production function can not model. Examples of these factors include experience curve effects, organizational learning, and complex yield relationships that affect the number of good die per wafer or the number of wafers that even make it through the process. Another complicating factor is that the output and inputs are changing rapidly over time, making it very difficult to accurately relate the two.

Hayes, et. al. [6] have proposed Total Factor Productivity (TFP) as a useful way to measure factory performance. TFP draws upon some of the principles of production theory. Productivity is a measure of the efficiency with which inputs are translated into outputs. Whereas single factor productivity (sfp) relates the total output to a single input, such as a particular type of raw material, TFP integrates and summarizes the contributions of all the factors of production (according to their contribution to total cost). TFP's main advantage is that it gives managers an integrated perspective on performance by incorporating the trade-offs between various inputs. The basic idea of relating a semiconductor fab's output, as measured by good die, to various inputs, such as labor, using some kind of productivity measure was particularly helpful in analyzing the data gathered from the Intel fabs.

## 3.3 Literature Review of Capacity Expansion

Capacity expansion is the addition of facilities or equipment to serve some need. Capacity expansion problems arise in a myriad of applications, including communications networks, gas and oil pipelines, public facilities, and manufacturing facilities. The primary capacity expansion decisions typically involve the sizes of facilities to be added and the times at which they should be added. Other major considerations include the type of capacity or the location of the capacity to be added.

There is a rather extensive literature available on capacity expansion and capital investment decisions. This is a basic problem in all industries, especially growing industries, hence much attention has been devoted to it. This section of the thesis reviews some of the more important aspects of the literature and theory concerning capacity expansion and focuses on those parts that are especially relevant to the research. Since the research focuses on individual fabs, capacity expansion literature that discusses the addition of equipment at a single site is the most relevant.

The process of making a capacity expansion decision in the traditional capital budgeting sense is quite straightforward and can be found in any finance textbook. Future cash inflows over the

lifetime of the project are forecasted, discounted and weighed against the discounted cash outflows required for the investment. The net present value is then compared to other investment projects available to the firm, or alternatively, a return on investment (ROI) figure is calculated using the same discounted cash inflows and outflows and compared to the firm's desired rate of return - or hurdle rate. If the ROI is larger than the internal hurdle rate and there are sufficient funds, the project is approved. If the ROI is smaller than the hurdle rate or there are not sufficient funds, the project is not approved.

What other criterion are used to guide capacity expansion decisions. In addition to calculating and comparing discounted cash flows, there are other financial and non-financial objectives. They include:

- 1. maximizing market share

- 2. maximizing capacity utilization

- 3. maximizing profit

- 4. minimizing costs such that projected demand is met

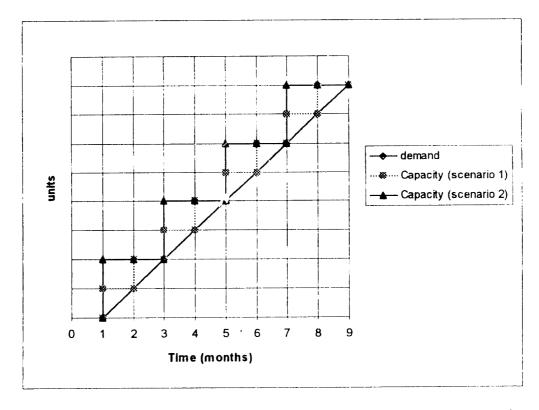

Figure 3.1 illustrates the strategy of maintaining a capacity cushion during a factory start-up, or capacity ramp. The capacity cushion represents excess capacity that the factory can use to respond to sudden demand surges or to ensure that projected demand for the factory's products is always met. In both scenarios in Figure 3.1 capacity leads demand. Scenario 1 illustrates the case where small increments of capacity are added relatively frequently. Scenario 2 illustrates a strategy where larger increments of capacity are added less frequently than in scenario 1.

Figure 3.1 Capacity Expansion Strategy Where Capacity Leads Demand

The capacity expansion problem has been modeled analytically for specific situations. Freidenfelds [7] provides a comprehensive discussion and derivation of many of the analytical models. Readers should note that the remainder of this section draws heavily from chapter 3 of Freidenfelds [7]. In general, models for the capacity expansion problem are restricted to situations in which the following apply:

- 1. The cost of the equipment or facilities added exhibits economies-of-scale (i.e., their cost is less than proportional to size). Stated another way, any addition of capacity is accompanied by some fixed costs.

- 2. Time is an important factor. That is, there is a continuing (possibly changing) need for facilities, and the facilities or equipment added are durable (i.e., they provide service over more than a short time interval).

One of the simplest analytical models for analyzing the capacity expansion problem is one in which a single capacity type, or piece of equipment, is to be added to serve a known deterministic demand. Since we are adding only a single capacity type, the production sequence only has one stage. The model assumes that the demand for additional units of capacity will grow linearly at rate g over an unbounded horizon, so that starting from time t=0, gt additional units will be required at time period t in the future. Typically, additional units of capacity are purchased in bulk, either because they only come that way or because it makes economic sense to purchase them that way. The model also assumes that the cost of additional units consists of a fixed cost A plus a linear cost B per unit of capacity, so that x additional units cost A + Bx, where x is a variable for the amount of capacity. A + Bx is the present discounted cost of providing x units of capacity forever. Graphically, this model can be represented on an x-y graph (see Figure 3.1), where the x axis is time and the y axis is demand or capacity in units. The demand line is a straight line with slope g and the capacity line is a stairstep function that is always above or equal to the demand line.

At this time the reader should note that the straight line representing the demand curve in Figure 3.1 looks very similar to the growth in wafer starts - wafers started into the production process - experienced by a ramping semiconductor fab. This similarity will be used in later sections to more fully explore the semiconductor fab start-up.

The simple model can be solved to find the values that result in demand being satisfied at all times with minimal discounted cost. Assuming that we can continue to place additional facilities in the indefinite future at the same cost, it should be clear that we always shall wait until existing facilities are full and then place some facility of size x, called the relief size. We wait until the facilities are full because it is better to spend later by the present value criterion. However, in some cases the company may not wish to wait until utilization reaches 100% before additional capacity is added. To include this more complicated dimension into the problem requires an additional concept - congestion cost. While there are more advanced capacity expansion models that do include congestion cost, they will not be used here due to their mathematical complexity. In the simple model we always use a facility of the same size in this formulation because the costs

and the projections of additional demand are identical at every shortage time. We wish to find the x that minimizes

$$C = \sum_{n=0}^{\infty} (A + Bx)e^{-r(nx/g)}$$

(3.1)

where the nx/g are the times at which additional equipment will be placed. Equation 3.1 represents the total discounted cost of capacity addition from time t=0 to infinity. With a positive discounting rate r, the sum converges to

$$C = \frac{A + Bx}{1 - e^{-r(x/g)}}$$

(3.2)

It is simple to show that C is a well-behaved convex function for positive x and so takes on a unique minimum. We can also rewrite equation 3.2 to show how C varies with the relief time interval, t. Substituting t=x/g, results in:

$$C(t) = \frac{A + Bgt}{1 - e^{-rt}} \tag{3.3}$$

Unfortunately, it is not possible to write an explicit formula for the x or t that minimizes C. The best that we can do is to get an implicit formula. If we set the derivative of C with respect to t to zero and rearrange terms, we obtain

$$e^{rt} - rt - 1 = \frac{Ar}{Bg} \tag{3.4}$$

The t that satisfies this equation is the optimal relief time. While we cannot explicitly solve for t, we can obtain a useful approximation. If rt is small,  $e^{rt}$  can be closely approximated by a second-order Taylor series expansion:

$$e^{rt} \approx 1 + rt + \frac{1}{2}(rt)^2$$

(3.5)

Combining these last two equations, we obtain

$$\frac{1}{2}(rt)^2 \approx \frac{Ar}{Bg} \tag{3.6}$$

or

$$t \approx \sqrt{\frac{2A}{Bgr}} \tag{3.7}$$

$$x = gt \approx \sqrt{\frac{2Ag}{Br}} \tag{3.8}$$

In general this approximation is considered fairly good if rt is small. In later chapters of the thesis, these equations are used to generate optimal equipment installation schedules - for those cases, rt is no greater than .075. The exact value for e<sup>rt</sup> if rt is .075 is 1.0779; the approximate value from the Taylor expansion is 1.0778. The approximated value is within .0066% of the actual value. If rt is large or greater accuracy is desired, equation 3.4 can be solved explicitly using numerical techniques. These equations are useful as rules-of-thumb guide to scheduling capacity additions for this particular case of linear demand growth, which assumes that manufacturing is carried out in a single stage process.

It is interesting to note the similarity of this capacity expansion model with inventory problems. Readers with some knowledge of inventory theory will recognize that the square root formula above is identical in form with the classical formula for economic order quantity. The similarity is not mere coincidence. The economic order quantity (EOQ) model is the simplest and most fundamental of all inventory models. It describes the important trade-off between fixed order costs and holding costs. Instead of fixed order costs and holding costs, the simple capacity expansion model discussed above optimizes the trade-off between fixed costs and the proportional cost of additional capacity. Both the simple capacity expansion model and the EOQ model use cost minimization as the optimization criterion.

Careful consideration of capacity expansion decisions show that they are very complex in nature. The decision involves not only financial considerations, such as discounted cash flows and rates of return, but also strategic and competitive analysis and the potential impact of the investment on the firm's people, infrastructure, and current capabilities.

#### 3.4 Overview of Semiconductor Device Fabrication

The transistor, which was invented in late 1947, and the integrated circuit, which was demonstrated around 1960, are the basis for today's microelectronic industry. Semiconductors have become the foundation for electronic devices because their electrical properties can be altered by adding controlled amounts of selected impurity (dopant) atoms into their crystal structures. While the first electronics devices were fabricated using germanium, silicon has become the industry standard.

The creation of the integrated circuit and the use of planar technology allowed for an ever increasing density of devices on silicon substrates. The idea of planar technology was to fabricated patterned layers, one on top of the other, made of materials with different electrical properties. The multidecked sandwich of patterned layers are made to form various circuit

elements such as transistors, capacitors, and resistors, and these are connected together by a patterned conducting layer to form an integrated circuit.

The layers are formed by modifying the substrate or depositing a layer of material on the substrate. Examples of substrate modification processes include doping and oxidation. Material can be deposited by evaporation or sputtering. Patterning is usually accomplished by the process of photolithography. The typical processes used to make integrated circuits are [8]:

- 1. oxidation

- 2. lithography

- 3. etching

- 4. diffusion and ion implantation

- 5. thin film deposition

Each of these processes are discussed in the remainder of this section.

The fabrication of integrated circuits takes place on silicon substrates possessing very high crystalline perfection. The process for making silicon wafers begins with quartzite. Quartzite, a type of sand, is refined by a complex, multi-stage process which produces electronic grade polysilicon. This polysilicon is used to grow single crystal silicon by Czochralski (CZ) crystal growth. In CZ growth, single crystal ingots are pulled from molten silicon contained in a crucible. The molten silicon contains controlled amounts of impurities which are incorporated into the cylindrical single-crystal ingot which results from the pulling process. The ingot is typically 100-200 mm in diameter and over 1 meter in length. After a single crystal silicon ingot has been grown, a complex sequence of shaping, sawing, and polishing steps must be performed on it to produce silicon wafers suitable for fabricating semiconductor devices. Device fabrication takes place over the entire wafer surface and hundreds of identical chips are created on each wafer at the same time.

The formation of the oxide of silicon (silicon dioxide) on the silicon surface is termed oxidation. A silicon dioxide layer is usually formed on the silicon substrate by the reaction of oxygen with the substrate material at elevated temperatures (900-1200 C). Some of the functions of the oxide film include dopant masking, device isolation, surface passivation, and use as a gate oxide. Oxide thicknesses can vary from tens to thousands of angstroms. The thermal oxidation process is fairly well understood and thicknesses can be controlled fairly well.

Lithography is the process by which the patterns that define the devices on the chip are transferred to the substrate surface. In the lithography process, the pattern in the form of a photomask is projected onto a surface that has been previously coated with a photoresist layer. Positive photoresist materials have two properties. First, when exposed to ultraviolet light, their solubility in one class of solvents is changed, so that after immersion in such a solvent the projected pattern is replicated in the surface. Second, the undissolved regions of the resist are not affected by a second class of etching agents, which are able to etch or modify the underlying material. After the wafer has been coated with photoresist, the photomask and wafer are aligned in a stepper. After alignment, they are subject to UV radiation. The exposed areas of photoresist

are then developed and the wafer is ready for the next process step. A wafer goes through the lithography process from ten to twenty times. The lithography process is critical because it defines the size of the smallest feature on the silicon substrate. Improvement in integrated circuit performance is driven by ever smaller feature sizes. Today, minimum commercially feasible feature sizes range from 0.35 to 0.5 microns.

Etching in semiconductor fabrication is a process by which material is removed from the silicon substrate or from the films on the substrate surface. The film can either be removed via wet etching or dry etching. Etch processes are measured by their selectivity and isotropy. The selectivity of an etched process is the ratio of etch rates of different materials. Any etch process must effectively etch the silicon or film layer with minimal removal of the underlying silicon or resist material. Therefore, a high selectivity is desired. When etching proceeds in all directions at the same rate, it is said to be isotropic. If etching proceeds exclusively in one direction, the etching process is said to be completely anisotropic. Vertical etch profiles are desired, hence anisotropic etching is favored.

The diffusion of controlled impurities or dopants into silicon is the basis of device formation and fabrication in integrated circuit processing. The dopants affect the electrical characteristics of the silicon material. Dopants are selectively introduced into the substrate by the diffusion or ion implantation processes.

In the diffusion process, impurities are introduced into the substrate by chemical sources. The chemical sources include gas, liquid, and solid forms. The dopants are then diffused to the desired depths by subjecting the wafers to elevated temperatures (900-1200 C). The depth is determined by time, temperature, and the diffusion coefficient of the dopant species in the substrate material.

Ion implantation has become the major means for the introduction of impurities into the substrate. Ion implantation is capable of placing the dopant species very precisely, but a diffusion step is still required to drive the impurities to specified depths, to electrically activate the implanted impurities, and to remove defects from the implantation area by annealing. Implantation is achieved by accelerating charged dopants through a high voltage field (10-1000 keV) and then choosing the desired dopant by means of a mass separator. Ion implantation is favored over chemical doping and diffusion methods because of its ability to implant exact quantities of dopants at specified depths below the surface in the designated areas of the substrate.

A large variety of thin films are used in the fabrication of integrated circuits. Examples of thin films used in semiconductor fabrication include polysilicon, silicon nitride, aluminum, and silicides. Thin films can be formed in many different ways. The film growth techniques can be divided into two groups: 1) film growth by interaction of vapor-deposited species with the substrate, and 2) film formation by deposition without causing changes to the substrate material. The first group includes thermal oxidation and nitridation of single crystal silicon and polysilicon and the formation of silicides by direct reaction of a deposited metal and the substrate. The second group includes chemical vapor deposition, in which solid films are formed on a substrate by the chemical reaction of vapor phase chemicals that contain the required constituents, and physical vapor deposition, in which the species of the thin film are physically dislodged from a source, to form a

vapor which is transported across a reduced pressure region to the substrate, where it condenses to form the thin film. Physical vapor deposition can be accomplished by sputtering and evaporation.

Once the individual devices have been fabricated on the wafer surface, interconnections are required to form a complete and functional integrated circuit. Interconnections are made of metals, such as aluminum, that exhibit low electrical resistance and good adhesion to dielectric insulator surfaces. The metal is deposited by physical vapor deposition techniques such as sputtering or evaporation. Today's integrated circuits have 2-5 layers of metallization with an insulating dielectric layer separating each metal layer. The interconnect layers are connected through the insulating layers by vias. Contacts establish the connection between the metal layer and the active devices in the silicon.

After metallization, a passivation layer is deposited on the wafer to protect the integrated circuit from the environment. Each of the chips is then tested using an electrical tester. After testing, the individual integrated circuits are separated from the wafer and sorted. The good chips are then packaged and tested one last time.

## 3.5 Characteristics of Semiconductor Manufacturing Systems

Semiconductor manufacturing systems represent a unique class of manufacturing systems. They are among the most complex and capital-intensive of all manufacturing processes. Semiconductor manufacturing systems are typically classified as job shops. Both semiconductor manufacturing systems and job shops are characterized by physical groupings of similar types of equipment or machinery, as opposed to transfer lines where there is a well-defined progression of product through the manufacturing system. Semiconductor manufacturing systems are characterized by:

- 1. high variability

- 2. reentrant material flows

- 3. batching of product

There are several sources of variability. One source of variability is low yields. During the start-up of a new semiconductor fab that is using leading-edge process technology, less than 50% of the chips that begin the process are functional when they reach the end of the process. Rework of product at various steps in the semiconductor manufacturing process also makes it difficult to predict system performance. In addition, typical machine uptimes range from 70 to 90%. Low availabilities typically require that extensive in-process inventory be maintained to buffer against machine downtimes, which leads to high throughput times and slow information turns. Since most of the testing takes place at the end of the semiconductor manufacturing process, some problems are not caught until large amounts of product have gone through the process and are affected by the same problem. Most of the difficulties arise from the fact that most semiconductor processes and equipment, especially those used to produce leading-edge chips, are not well understood.